在电子系统中,时钟信号是系统动手的“心跳”,而晶体谐振器与晶体回荡器则是生成这一“心跳”的中枢元件。尽管两者均基于石英晶体的压电效应,但它们在结构、功能和运用场景上存在骨子各别。本文将从旨趣、本性、运用及选型战略四个维度,系统领略两者的远隔。

一、界说与组成:被迫元件与有源模块的骨子各别

晶体谐振器(Crystal Resonator)

晶体谐振器是纯粹的被迫元件,其中枢为石英晶体片,通过压电效应终了机械振动与电信号的调治。它仅能提供谐振频率的基准,自己无法径直输出时钟信号,必须依赖外部电路(如放大器、响应相聚和负载电容)才智酿成回荡。举例,在单片机系统中,晶体谐振器需与两个外部电容匹配,组成并联谐振回路,才智驱动回荡电路责任。

晶体回荡器(Crystal Oscillator, XO)

晶体回荡器则是圆善的有源模块,里面集成了晶体谐振器、回荡电路、放大器和输出驱动电路。它通过踏实供电即可径直输出方波或正弦波形貌的时钟信号,无需罕见联想外围电路。高端晶体回荡器还可集成温度抵偿(TCXO)、电压阻抑(VCXO)或恒温阻抑(OCXO)等功能,以应酬环境变化对频率踏实性的影响。

二、责任旨趣:外部驱动与里面集成的本领分野

晶体谐振器的责任旨趣

晶体谐振器依赖外部电路驱动,其频率由石英晶体的机械振动本性决定。通过养息负载电容(如两个外部电容)的值,不错微调谐振频率。商酌词,这种养息样式对电路布局和元件精度要求较高,且频率踏实性受外部电路联想影响较大。举例,在大约时钟源运用中,晶体谐振器需与外部电容酿成谐振回路,但若电容值不匹配,可能导致频率偏移或回荡失败。

{jz:field.toptypename/}晶体回荡器的责任旨趣

晶体回荡器里面已固化回荡要求,AG百家乐APP官方网站启动后可快速输出高踏实性的时钟信号。其中枢上风在于里面集成的回荡电路,该电路通过响应机制保管踏实的回荡现象,无需外部元件扰乱。举例,在通讯开导中,晶体回荡器可径直输出适合圭臬的时钟信号,确保数据传输的同步性。

三、本性对比:资本、功耗与踏实性的量度

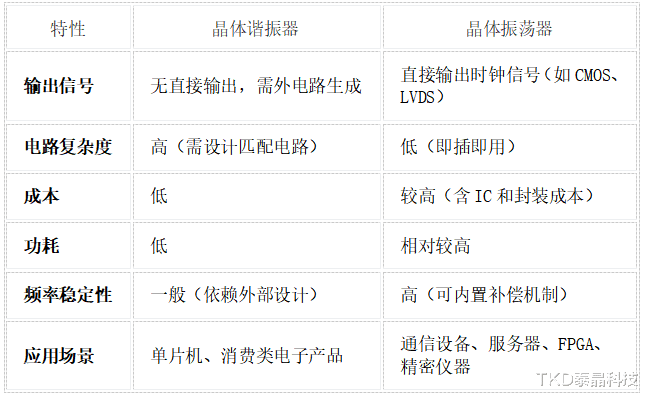

从表中不错看出,晶体谐振器在资本和功耗上具有上风,但频率踏实性较差;而晶体回荡器则以高踏实性、低电路复杂度为特色,但资本和功耗相对较高。

四、运用场景:大约时钟源与高精度系统的需求各别

晶体谐振器的运用场景

晶体谐振器适用于资本明锐、联想目田度高的场景,举例:

单片机(MCU)的时钟源:在镶嵌式系统中,晶体谐振器通过外部电容匹配,为MCU提供基础时钟信号,米兰体彩下载知足系统动手的基本需求。

低复杂度电子开导:如家用电器、玩物等,对时钟精度要求不高,晶体谐振器可镌汰联想资本。

晶体回荡器的运用场景

晶体回荡器则适用于对踏实性、集成度要求高的场景,举例:

通信开导:在5G、Wi-Fi模块中,晶体回荡器提供高精度的时钟信号,确保数据传输的同步性和可靠性。

做事器与FPGA:在数据中心和高性能野心限度,晶体回荡器的高踏实性可幸免因时钟偏差导致的系统故障。

精密仪器:如GPS、雷达等,对时钟精度要求极高,晶体回荡器通过内置抵偿机制,确保在复杂环境下仍能踏实责任。

五、选型战略:资本、踏实性与开导成果的均衡

选择晶体谐振器的要求

联想空间大且资本明锐:住持具对资本阻抑要求严格,且联想团队具备高频电路调试智商时,优先选择晶体谐振器。举例,在耗尽类电子家具中,晶体谐振器可通过外部电容匹配,终了低资本时钟源。

运用场景对时钟精度要求不高:如已往MCU时钟源,晶体谐振器可知足基本需求,无需罕见联想抵偿电路。

选择晶体回荡器的要求

追求高踏实性与快速开导:住持具对时钟精度要求高,或开导周期病笃时,优先选择晶体回荡器。举例,在通讯开导中,晶体回荡器可径直输出适合圭臬的时钟信号,减少硬件调试时分。

高集成度需求:在做事器、FPGA等复杂系统中,晶体回荡器的即插即用本性可简化联想经过,镌汰开导风险。

六、转头:从“原材料”到“制品”的互补关联

晶体谐振器与晶体回荡器的关联,可类比为“原材料”与“制品”的互补。前者是基础元件,需外部电路和谐才智责任;后者是集成化模块,径直提供圆善时钟信号。两者在资本、复杂度、精度上酿成互补,联想者可字据具体需求选择:

资本优先:选择晶体谐振器,自行联想回荡电路;

踏实性优先:选择晶体回荡器,即插即用,减少联想风险。

在电子系统联想中,领悟晶体谐振器与晶体回荡器的骨子各别,是优化时钟信号生成的纰谬。通过合理选型,可终了资本、性能与开导成果的均衡,为系统踏实动手奠定基础。